# JOURNAL

#### table of contents

December 1994, Volume 45, Issue 6

## **Articles**

Fast DDS-2 Digital Audio Tape Drive by Damon R. Ujvarosy

DDS-2 Tape Autoloader: High-Capacity Data Storage in a 5 1/4-Inch Form Factor by Steven A. Dimond

**Automatic State Table Generation** by Mark J. Simms

**Using State Machines as a Design and Coding Tool**

by Mark J. Simms

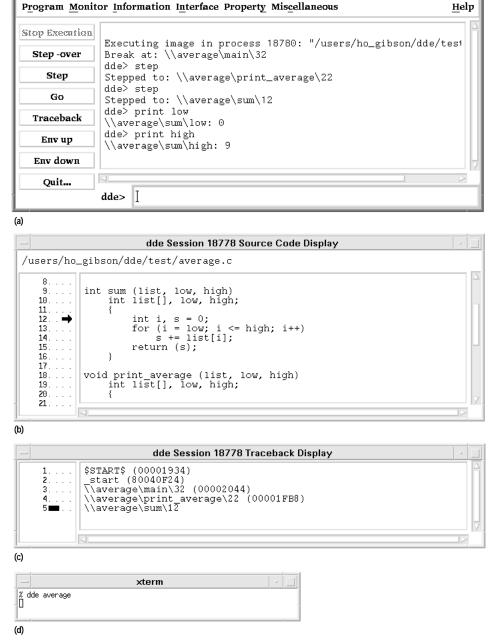

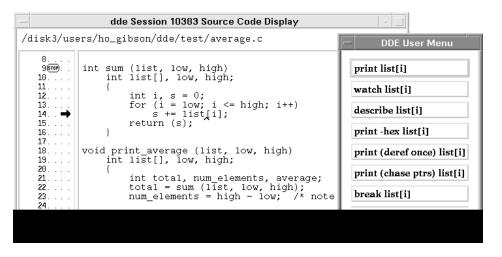

An Event-Based, Retargetable Debugger by Arun K. Iyengar, Thaddeus S. Grzeski, Valerie J. Ho-Gibson, Tracy A. Hoover, and John R. Vasta

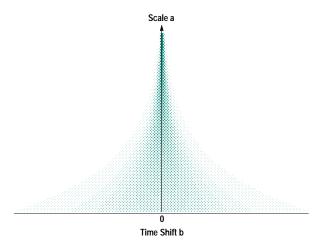

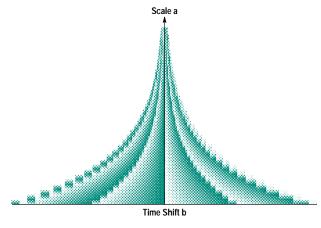

**Wavelet Analysis: Theory and Applications** by Daniel T. L. Lee and Akio Yamamoto

Approaches to Verifying Operational Test Release Vectors by Joy Xiao Han

8

**Estimating the Value of Inspections and Early Testing for Software Projects** *by Louis A. Franz and Jonathan C. Shih*

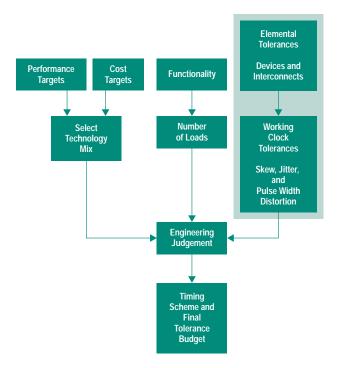

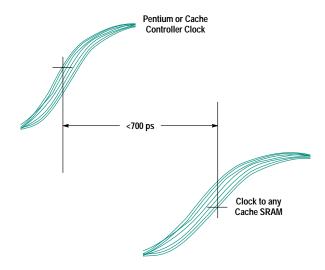

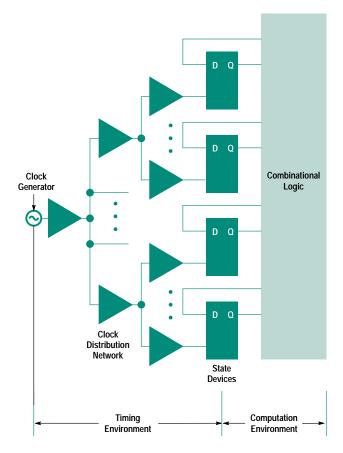

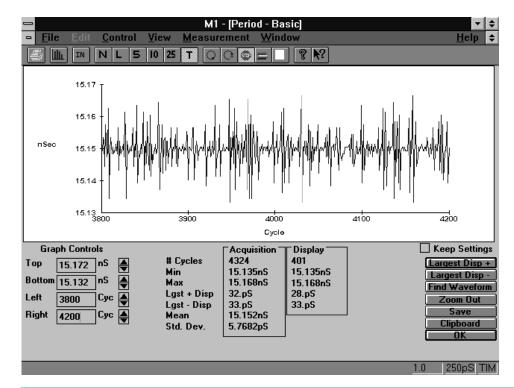

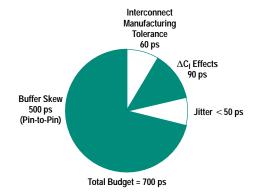

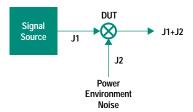

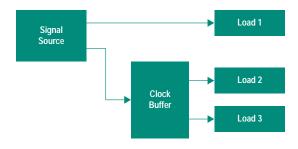

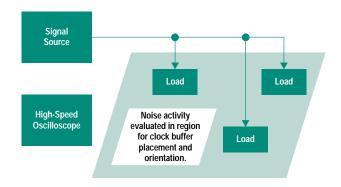

Clock Design and Measurement Issues in Pentium(TM) Systems

by Michael K. Williams and Andreas M.R. Pfaff

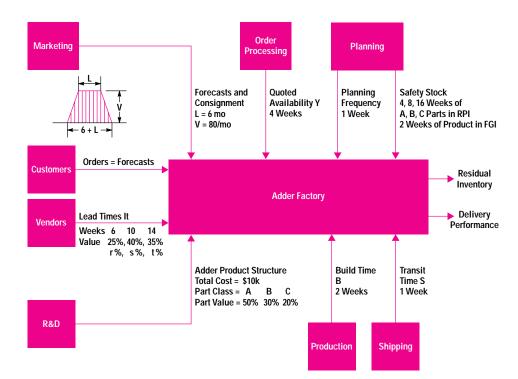

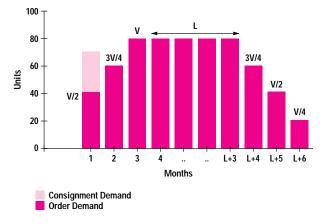

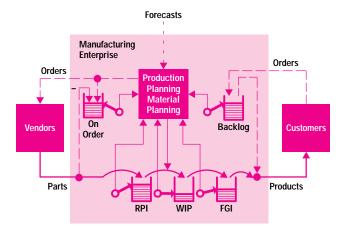

# Enterprise Modeling and Simulation: Complex Dynamic Behavior of a Simple Model of Manufacturing by M. Shahid Mujtaba

# Fast DDS-2 Digital Audio Tape Drive

Running at a data transfer rate of 510 kbytes/s, the HP C1533A tape drive can record a full 4-Gbyte DDS-2 cartridge in just over two hours, almost an hour less than typical DDS-2 drives. Its development required improvements in tape material, length, and thickness, new read and write heads, a new drum design, and new methods for linearity measurement and adjustment.

#### by Damon R. Ujvarosy

Like all aspects of computing today, the face of mass storage is changing rapidly. Only a few short years ago, gigabytes of disk storage was the domain of large computer systems, housed in computer rooms with dedicated staff to look after the equipment. Personal computers that had more than 100 megabytes of disk storage were a rarity, and networks were just coming of age. The individual computer user rarely considered backup. Critical data was kept on large computer systems and backup to tape was handled by the MIS department. The odd file on the PC that was important could be saved on a diskette.

Times have changed rapidly. Individual PCs with several hundred megabytes of disk storage are common. Network servers for PCs and workstations have multiple gigabytes of disk storage. The data on these disks is critical to the company's business. High-performance, high-capacity backup solutions that fit the needs of today's computer systems are essential

The same technologies that are propelling disk drive capacity and performance are also being applied to tape drives. Tape drives that meet the backup needs of the individual PC user are available using the DC2000 minicartridge—for example, the HP Colorado Memory Systems Jumbo 250 and Jumbo 700 tape drives. However, the backup needs of the network server are far greater. These larger backups also

require improved performance to complete the data backup in a reasonable time.

The Digital Data Storage (DDS) format standard was developed by HP and Sony in the late 1980s to establish a capacity and performance point that would serve the emerging network server market as well as the more established small multiuser systems market. The DDS format standard is based on the Digital Audio Tape (DAT) standard, which uses 4-mm-wide tape. Tape drives that employ the DDS format standard are therefore often referred to as DAT or 4-mm tape drives.

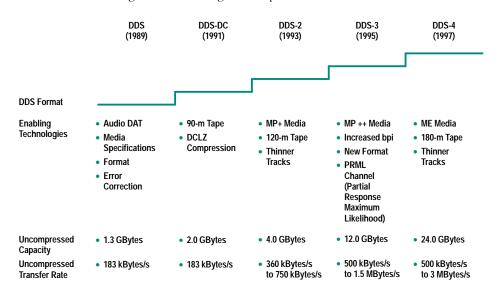

In HP DAT drives, lossless data compression was added later to the DDS format standard using an HP-developed method called DCLZ,<sup>1</sup> an implementation of a technique known as Lempel-Ziv data compression.<sup>2</sup> DCLZ effectively doubled the capacity and performance of the tape drive, and at the same time, longer tapes were added. Four gigabytes could then be stored on a single DDS tape. Further extensions to the DDS format standard that will allow the DDS format to serve the backup needs of network servers through the end of the 1990s have been agreed to by the DDS manufacturers group (see Fig. 1).

The HP C1533A DDS-2 tape drive (Fig. 2), introduced in 1993, stores eight gigabytes of data (typical capacity

**Fig. 1.** Evolution of the DDS tape format.

**Fig. 2.** The HP C1533A DDS-2 tape drive has a native-mode data transfer rate of 510 kbytes/s, 40% faster than other designs. It records on high-capacity 4-Gbyte DDS-2 cartridges or on earlier DDS media.

achieved using the DCLZ data compression standard) and has a data transfer rate more than 2.5 times that previously available on DDS tape drives. The HP C1533A not only reads and writes tapes based on the DDS-2 format standard, but is also able to read and write tapes based on the original DDS format standard to provide compatibility with the large installed base of DDS tape drives already in existence.

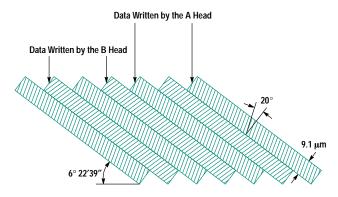

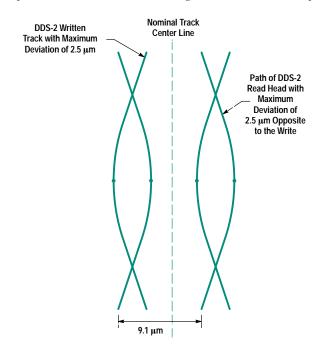

The DDS-2 format standard calls for the data to be written on tracks that are nominally 9.1  $\mu$ m wide as opposed to the previous DDS format standard, which used a 13.6- $\mu$ m track width. The DDS-2 format standard also makes use of tapes that are 120 m long rather than the previous 90-m and 60-m tapes. These changes, defined by the DDS-2 format standard, along with a data transfer rate increase to 510 kbytes/s from 183 kbytes/s (the data transfer rate seen by the user is effectively doubled to over 1 Mbyte/s by the use of data compression) required numerous technical developments.

#### Media

The media used for DDS-2 are an enhancement of the existing DDS 60-m and 90-m media. Physically, all three cartridges look similar; they use the same cartridge shell and are all designed to meet the same environmental and data reliability specifications. What differentiates them, apart from the packaging, is the length of tape in the cartridge shell and the signal characteristics or recording properties of the media. The tape drive differentiates between the cartridge types by the use of recognition holes in the cartridge shell.

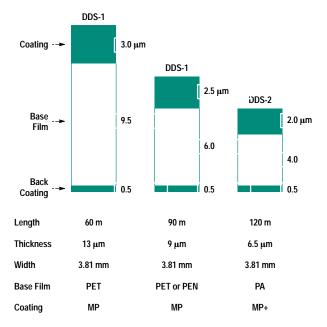

The longer tape length is achieved by reducing the total thickness of the tape so that the tape pack volume is the same for 120 m as for 60 m and 90 m. Fig. 3 shows the relative thicknesses of the three DDS media types and a simplified view of the construction of the tape. To provide optimal head-to-tape contact when switching between the different tape thicknesses (the drive needs to read and write DDS-1 tapes as well as DDS-2 tapes) the stiffness of the tapes needs to be matched as closely as possible. However, because the relationship between tape thickness and stiffness is a cubed law, use of the same base film material is not possible. A new base film material, polyamide or PA, has been developed. It has high stiffness, and by careful design of the

**Fig. 3.** DDS tape types. MP = metal particle. PET = polyethylene terathalate. PEN = polyethylene naphtalate. PA = polyamide.

heads and drum, the ability to switch from one tape type to another can be optimized.

The 120-m tape, at 6.5- $\mu$ m total thickness, offers the thinnest media currently in use in the data recording industry. This has necessitated improvements in the accuracy of the tape guidance system within the tape mechanism and in the tape motion tension control servo of the mechanism to prevent media damage.

The use of thinner tracks reduces the overall system signal-to-noise ratio and the tape was called upon to make a contribution to reducing the deficit. An increase of +3 dB over the existing DDS media was needed. Existing 60-m and 90-m media use metal particle (MP) coatings. To meet the additional signal requirements an enhanced MP tape has been developed and has been designated MP+. By using a combination of magnetic particle size reduction, increased coercivity, increased remanence, and reduced surface roughness of the media, the additional signal requirements were achieved.

The higher head-to-tape speed of the HP C1533A DDS-2 tape drive compared to previous DDS drives places additional constraints on the media. Without efficient lubrication the surface of the media is damaged reducing the life of the media. There is also the possibility of the heads becoming clogged with debris from the media. To reduce this effect the lubrication has been modified for DDS-2.

#### Heads

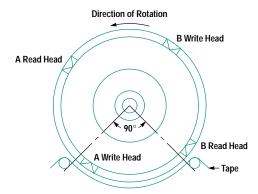

The changes needed for DDS-2 also called for modifications to the heads. A DDS tape drive has four heads mounted on a rotating drum. Two heads are used for writing and two for reading. The tape is wrapped around the drum over an angle that is nominally 90 degrees (see Fig. 4) so that only one head is in contact with the tape at any given time.

During a write, the first write head (designated the A write head) contacts the tape and data is written with an azimuth angle of +20 degrees. The first read head (designated the A read head) contacts the tape next to verify the previously

Fig. 4. The DDS tape drive has four heads mounted on a rotating drum. Only one head at a time is in contact with the media.

written data. The second write head (designated the B write head) contacts the tape next to write data with an azimuth angle of -20 degrees. The second read head (designated the B read head) contacts the tape next to verify the data previously written by the B write head. During this process the tape is moved forward to produce data on the tape as shown in Fig. 5.

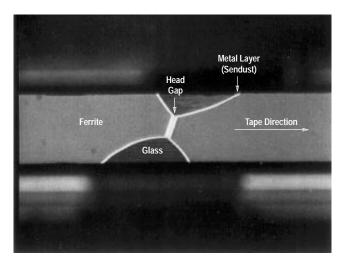

To accommodate the higher coercivity of the DDS-2 tape media the write head was changed from a Sendust†-based head to a metal-in-gap (MIG) style ferrite-based head (see Fig. 6). The MIG head ensures that the magnetic coating on the tape is fully saturated during the write process. Sendust is still used in the head, but only for the gap metal and not as the bulk material.

The read head required several changes to meet the needs of the HP C1533A. The first was to change from a Sendust-based head to a ferrite-based head. This was necessary to maintain the nominal head life specification of 6000 hours. Since the HP C1533A has a data transfer rate that is 2.87 times the previous generation of DDS tape drives, the head is in contact with the tape media 2.87 times more during that 6000 hours. The ferrite-based head is harder than the Sendust-based head and meets the life requirements.

The second change to the read head was to the width. The nominal width of the read head for the DDS format standard was  $20.4~\mu m$ . A read head of this width on a  $9.1~\mu m$  wide DDS-2 track would allow too much adjacent track noise to

† Sendust is an alloy of 85% Fe, 6% AI, and 9% Si. It was developed at the University of Sendai, Japan.

Fig. 5. DDS-2 track format on tape.

Fig. 6. The HP C1533A tape drive has metal-in-gap ferrite-based write heads.

be picked up, thereby reducing the signal-to-noise ratio below an acceptable level. At first glance it would seem that a read head width of 9.1  $\mu m$  (equal to the nominal written track width) would be optimum (maximum on-track signal pickup with minimal adjacent-track noise pickup). This would be valid if the tracks were all perfectly straight. However, the DDS-2 standard calls for the tracks to be straight within ±2.5 µm over the length of the track (called linearity) to allow for mechanical tolerances in the tape drive. While a 9.1-µm-wide read head would provide an excellent signal-tonoise ratio on a perfectly straight DDS-2 written track, it would not be able to read a worst-case DDS-2 written track that was written by a different drive (see Fig. 7). In this case, the read head would have a large adjacent-track noise pickup with a relatively small on-track signal pickup. Since the ability to interchange tapes between tape drives was an important consideration in the design of the HP C1533A tape

**Fig. 7.** Effects of tape and drive nonlinearity when a track written by one drive is read by a different drive.

drive, a balance needed to be struck to achieve the optimum read head width. A 12-µm read head width was specified through the use of computer modeling of the effect of adjacent-track noise on signal-to-noise ratio. Experiments verified the performance of the 12-µm head.

#### **Drum Design**

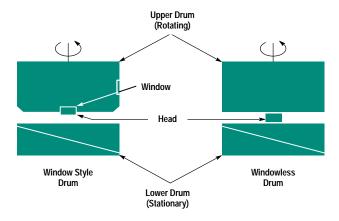

The next major challenge came in the drum design. The increase in the data transfer rate to 510 kbytes/s from 183 kbytes/s required an increase in the drum rotation speed, to 5737 r/min from 2000 r/min. The major issues to contend with were drum bearing life, acoustic noise at the higher rotation speed, and excessive air between the drum and the tape. Excessive air would force the tape too far away from the drum, resulting in reduced signal levels because of loss of contact between the head and the tape.

A great deal of work has already gone into bearing life and acoustic noise in high-rotation-rate spindle motors for disk drives. The key to bearing life is the proper choice of lubricants. By using the same high-performance lubricants that are found in disk drive spindle motors, we were quickly able to meet the bearing life requirements of the HP C1533A tape drive.

The acoustic noise generated by the drum is largely a function of the control system. The control algorithm used in the HP C1533A tape drive reduces the high-frequency content of the control signals so that the acoustic noise of the HP C1533A is comparable to previous-generation DDS tape drives.

The problem of excess air between the drum and the tape required the development of techniques to bleed away the excess air to ensure that proper head-to-tape contact was maintained. Several techniques were prototyped and carefully measured by HP Laboratories for their impact on tape deformation. Among the techniques prototyped was a "window-less" drum, in which there is a gap between the lower, stationary section of the drum and the upper, rotating section of the drum. The gap provides a path for the air to bleed away and eliminates the need for a "window" around the head. A second technique prototyped was a standard window style drum with a small chamfer along the bottom edge of the upper rotating section of the drum to provide the necessary air bleed (see Fig. 8).

In the end, the window style drum using a chamfer on the lower edge of the rotating section of the drum was found to be the best solution, ensuring that the tape was not damaged while providing an easily manufacturable solution to the problem of excess air between the drum and the tape.

#### Linearity

As previously mentioned, the DDS-2 specification calls for a maximum deviation from a straight line of  $\pm 2.5~\mu m$  for a written track. This specification is referred to as linearity. The linearity of the previous generation of DDS tape drives was measured and found to have a mean value of 3.7  $\mu m$  and a standard deviation of 0.74  $\mu m$ . To meet the DDS-2 specifications, an intensive research activity was undertaken at HP Laboratories. That research determined that the linearity measurement and adjustment process would have to be changed to meet the DDS-2 specifications consistently.

Previously, linearity was measured by writing a tape, physically cutting out a section of that tape, developing the tape using ferrofluids to be able to see the written tracks, and then measuring the tracks under a microscope. This technique suffers from two problems. First, the measurement error associated with the technique was found to be up to 2  $\mu m$ . Second, the technique did not allow the linearity to be measured in real time while adjustments to the guides were being made on the production line.

The problem of measurement error was tackled by developing an automated optical measurement system. Using optical pattern recognition software, the system automatically finds special written patterns on the tape. A precision coordinate measurement system measures the track position relative to the edge of the tape. The system is calibrated with a chrome optical standard and a measurement accuracy of  $\pm 0.15~\mu m$  is achieved.

This optical measurement system is used to measure the absolute linearity of tapes. These tapes are then used as a reference for a real-time measurement system in production. Special patterns written on the tape are used by the tape drive under test to measure its own deviation along the track relative to the tape in the drive. By subtracting out the measured linearity deviation of the tape in software, an accurate real-time measurement of the linearity of the drive under test is achieved. It is then possible for a production operator to adjust the tape guides for minimum linearity deviation as part of the standard production process. The use of these linearity measurement and adjustment methods has allowed HP to reduce the mean linearity deviation in production to 1.4  $\mu m$  with a standard deviation of 0.33  $\mu m$ , well within the DDS-2 specifications.

#### **Performance**

The network server market that the HP C1533A tape drive is designed to serve requires high performance as well as high capacity. The data transfer rate of 510 kbytes/s is an important factor in the performance of the HP C1533A tape drive since it defines the maximum rate at which data (after compression) can be written to or read from the tape. The actual

**Fig. 8.** Two styles of drums with gaps to bleed off excess air between the drum and the tape. In each case, four heads are spaced evenly around the drum, but only the one nearest the observer is shown in this drawing. The diagonal line on the lower drum is the path of the lower edge of the tape in this helical scan system.

performance the user will see in a system is a function of at least thirteen factors. Some of these factors are a function of the tape drive, but many are dictated by the system using the tape drive. The major performance factors, along with the corresponding controlling functions, are listed below.

#### **Performance Factor**

Data transfer rate

#### **Controlling Function**

Tape drive if desired data transfer rate is greater than maximum tape drive transfer rate

Computer system if desired data transfer rate is less than maximum tape drive transfer rate Tape drive

Maximum data compression ratio that maintains maximum tape drive transfer rate Data compression ratio Main buffer size SCSI transfer rate

Data

Tape drive

Limited to the maximum SCSI

transfer rate that both the

tape drive and the computer

system can achieve

Computer system

Data transfer size

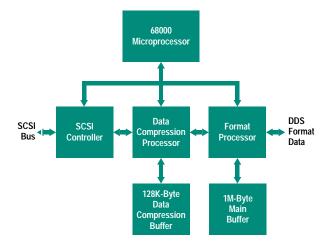

The architecture of the HP C1533A controller is outlined in Fig. 9.

An examination of the write process is instructive in understanding the potential performance limiters. The following are the major steps in the write process.

- 1. Computer system negotiates SCSI transfer rate with the tape drive.

- 2. Computer system establishes transfer size.

- 3. Computer system transfers data to the tape drive.

- 4. Tape drive compresses the data through the data compression processor and moves the data into the main buffer.

Fig. 9. Block diagram of the HP C1533A tape drive controller.

- 5. Format processor divides the data into DDS format standard groups and adds access and indexing data to enable high-speed search and retrieval and error correction fields to maintain data integrity on reads.

- 6. DDS format data is written onto the tape.

To achieve maximum performance, it is essential that DDS format data is available to write onto the tape at all times. If no data is available, the tape drive will have to stop writing data and wait until data is available before restarting the write process. The tape will also have to be repositioned before the next write can begin. The format processor must of course have the ability to take the data from the main buffer, convert the data into the DDS format and compute the error correction values in real time or the tape drive will never achieve its full performance.

The main buffer performs a speed matching function, giving the data compression processor the necessary freedom to output data at a varying rate while keeping the tape drive streaming. Modeling demonstrated that a buffer size of 1M bytes is sufficient to maintain the performance of the HP C1533A tape drive in most applications.

The maximum speed at which the data compression processor can take uncompressed input data and output it as compressed data is another factor in the performance picture. The more compressible the data, the faster the data compression processor needs to be to maintain an output rate that is fast enough to keep the tape drive streaming. An average compression ratio of 2 to 1 is the accepted industry norm for typical computer data. However, within a large backup, the compression ratio of individual files will vary tremendously. By studying a large number of backups, we were able to establish that the data compression processor needs to be capable of about 4-to-1 compression at full output rate to maintain an overall 2-to-1 compression rate. We therefore designed the data compression processor for the HP C1533A to meet this requirement.

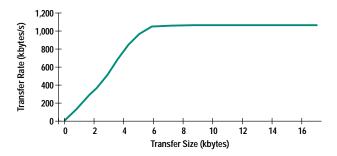

The last major piece in the performance picture has to do with the ability of the computer system to move data to the tape drive. To get the maximum performance from the tape drive, it is important that the computer system provide the data as fast as the tape drive needs it. The maximum rate at which the data can then be transferred to the tape drive is determined by the negotiated SCSI transfer rate and the transfer size that the computer system establishes. The SCSI transfer rate is the lower of the computer system and tape drive maximum rates. If the computer system's maximum SCSI transfer rate is less than the tape drive's maximum SCSI transfer rate, the SCSI transfer rate used will be that of the computer system. The slower the transfer rate, the less time there is to cover any system overhead. Additionally, if the computer system establishes a small transfer size, the data transfer will occur in small increments. Since each transfer has overhead associated with it, small transfer sizes will have relatively more overhead which will likely reduce the performance of the tape backup (see Fig. 10).

**Fig. 10.** Maximum data transfer rate of the HP C1533A tape drive at 2:1 data compression ratio (variable mode, writing from memory on an HP 9000 Model 720 computer).

#### Acknowledgments

I would like to acknowledge Hugh Rattray for mechanism and media development management, Peter Steven for tape path development, John Hardwick and Phil Connor for head and drum development, Ian Russell for media development, Simon Gittens for servo and data channel development management, Rob Morling for data channel development, Ben Willcocks for servo code development, Julian Potter for prototype and tool development, Tom Conway for servo IC development, Steve Krupa for controller development management, Tim Phipps, Andy Hana, Steve Langford, Pete Walsh,

and Dave Dewar for controller IC development, Richard Bickers, Paul Bartlett, Simon Rae, and Jon Buckingham for controller firmware development, Pete Bramhall for technology and standardization management, Chris Williams and Simon Chandler for data channel modeling, Bryan Magain for interchange test development, Richard Vincent for integration management, Dave Tuckett, Simon Southwell, and Jon Rushton for integration engineering, Greg Trezise and John Rich for printed circuit board development, Gary Marriner for project coordination, Mike Padfield, Malcolm Grimwood, and Jonathan Lord for testing, Carl Tausig of HP Labs, Palo Alto for linearity measurement tools, Albert Jeans of HP Labs, Palo Alto for tape path modeling, and many others. I would like to thank Ian Russell, Peter Steven, and Richard Bickers for their help in preparing the material for this article. I would also like to thank Jo Dursley for her efforts in typing and editing the article.

#### References

- 1. M.J. Bianchi, et al, "Data Compression in a Half-Inch Reel-to-Reel Tape Drive," *Hewlett-Packard Journal*, Vol. 40, no. 3, June 1989, pp. 26-31. This paper discusses the HP-DC algorithm, a precursor of the DCLZ algorithm.

- 2. J. Ziv and A. Lempel, "A Universal Algorithm for Sequential Data Compression," *IEEE TRansactions on Information Theory*, Vol. IT-23, no. 3, May 1977, pp. 337-343.

# DDS-2 Tape Autoloader: High-Capacity Data Storage in a 51/4-Inch Form Factor

The autoloader holds six 4-gigabyte cartridges. With data compression, it can back up typically 48 Gbytes of data overnight or 8 Gbytes every day for six days, unattended.

#### by Steven A. Dimond

The trend from centralized computing data centers to PCs and client-server networks has led to increased local or semilocal data storage and backup. As discussed in the preceding article, DDS tape drives are designed to meet these requirements. However, as network server disk capacities increase above the capacity of a single DDS tape (8 gigabytes for DDS-2, compressed), or if manipulation of the backup tapes becomes a chore, then there is a requirement for a larger storage device.

The type of person who carries out the backup has also changed with these trends in computing. The centralized data center had trained, full-time operators, whereas the network administrator or workstation user may not be formally trained and will want to spend the minimum time and effort completing the backup.

These requirements for storage capacity and ease of use have led to a need for an automated, easy-to-use, large-capacity tape device.

One way to add significant capacity at modest cost is to use a changer mechanism (robot) to select a tape from a library of tapes and put it into the tape drive. The changer mechanism may only double or quadruple the cost of the tape drive unit, but the capacity can increase many times more than this. There are tape libraries that have from 10 to 120 tapes and one or two built-in tape drives. The access times to select a tape are acceptable for a backup or library type application.

Given the emerging network requirements, there is an even bigger need for a small device that fits the standard "5¼-inch" peripheral slots. These are approximately 146 mm wide by 83 mm high by 203 mm deep (5.75 in by 3.25 in by 8 in). This is enough volume to hold a smaller peripheral-size tape drive and a changer mechanism.

These smaller devices that perform unattended backup are typically called autoloaders. At HP's Computer Peripherals Bristol division, we investigated this growing need. This investigation led to the development of the HP C1553A DDS-2 digital audio tape autoloader, Fig. 1.

The HP C1553A autoloader incorporates the HP C1533A DDS-2 tape drive described in the article on page 6. It holds six DDS-2 cartridges, each having a native capacity of four gigabytes. With data compression, each cartridge can hold typically eight gigabytes, giving the autoloader the ability to back up typically 48 gigabytes without operator intervention.

**Fig. 1.** The HP C1553A DDS-2 digital audio tape autoloader contains a DDS-2 tape drive and a cartridge changing mechanism that selects one of six cartridges from a magazine and loads it into the drive. Cartridges are changed automatically under software control.

Two standalone versions are available: The HP 6400 Model 48AL for HP 9000 workstations and the HP SureStoreTape 1200e for Novell Netware and Windows NT systems.

#### **Design Objectives**

The basic definition for the HP C1553A autoloader was very simple. It was to be a DDS tape autoloader, fit into a standard 5¼-inch peripheral enclosure, use a standard HP DDS drive with minimum (or no) modifications, use the drive's SCSI II interface, hold as many tapes as possible, and be reliable and ergonomic.

During the investigation phase for this product there were prototypes of similar products available. To keep the investment low we considered procuring one of these designs. However they fell short of some of the requirements, so the decision was made to produce our own design.

Given the small size of the product and the desire to accommodate as many tapes as possible, the interior space was at a premium. Despite frequent questioning by the engineers, the outside dimensions could not be increased if we were to be sure of satisfying the maximum number of customers. One possibility was to have a "power bulge" on the rear of the unit, but this was rejected because it might obstruct some customers' installations.

It was decided that the new HP C1533A DDS-2 tape drive was to be fitted inside the autoloader. For reasons of manufacturing simplicity and cost, the drive had to be used with minimum modification. We were also aware that the autoloader would be a platform for future DDS drives, so easy integration was important for future generations as well. The price of the autoloader could perhaps be only double that of the DDS-2 drive for several times the capacity.

The SCSI II interface of the built-in drive can be used to pass on control commands to the changer mechanism. Thus the customer need only use one SCSI bus ID where some libraries require two.

The more tapes the device can hold, the more attractive a product it will be. Competing autoloaders with four cartridges were known to be under development, so our goal was to match this number or exceed it.

We saw the magazine holding the tapes as a simple storage solution, that is, inexpensive and capable of being stored like a video tape. This allows the user to treat a magazine as a big single backup tape, rather than having to manipulate a lot of single tapes.

For reliability and ease of use, use models and metrics were developed. In the early stages of development, user tests were conducted on possible design concepts.

#### **Physical Architecture**

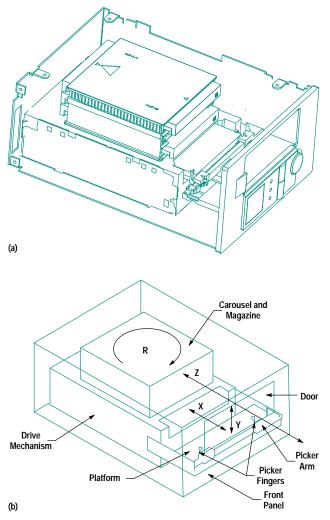

The physical architecture is dominated by the lack of space. Fitting the 3½-inch C1533A tape drive into the volume allowed for the autoloader accounts for much of the difficulty. The drive is placed at the rear of the autoloader volume because it has its interface connections at the rear and the tape loading at the front. There is just enough space for a tape in front of the drive, but unfortunately no front-to-rear room for a mechanism. However, removing the front panel (bezel) of the drive, which is not required, created a vital few extra millimeters.

The construction of the front of the DDS-2 drive is such that the tape can overlap the drive when it is ejected, that is, the tape can extend into the drive about 11 mm. This means that a tape must be moved vertically above the drive to remove it; it cannot move down through the drive mechanism. This allows just over 10 mm from the front of any tape to the autoloader front panel. This configuration also places the drive at the rear bottom of the autoloader so that access to other tapes is from above the drive.

This configuration does have some benefits. The drive connectors and option switches on the rear and bottom are directly accessible at the exterior of the autoloader. Thermally this is also the best arrangement because the drive base is exposed to the exterior air. The drive base is an important heat dissipation area just below the main controller printed circuit assembly. Finally, for integration and repair we were able to design the autoloader to accept the drive with a simple bracket arrangement and a single connecting cable.

The changer mechanism, controller printed circuit assembly, magazine, and door and front panel parts have to fit in the rest of the available space. At this point we checked again whether we could exceed the form factor, and were again asked to look inward rather than outward.

#### **Autoloader Control Electronics**

The autoloader control electronics were designed with the aim of linking the mechanism and firmware elements with low-risk, proven technology at low cost. The main controller printed circuit assembly is a through-hole design with a shape to suit the space available. The space envelope for the printed circuit assembly was derived directly from the mechanical CAD model because it was so tight. Control of the mechanism is managed by a Hitachi H8/325 microcontroller with on-board one-time-programmable (OTP) and RAM memories, nearly 90% of the pins being available for I/O. Logic-level pulse width modulation signals generated by the microcontroller control the dc motors and their integral gearboxes. Two-level motor current sensing is used to detect mechanical jams or excessive motor loading. The four motors and the picker solenoid are powered from the 12V supply available in 5½-inch peripheral slots.

The state of the mechanism is determined by optical means. For each motion, a mechanical part has a rib that is made to pass through slotted optical switches. The rib has slots at datum positions in the motion that are detected by the optoswitch. The width of each slot is calculated to reflect the mechanical tolerance of the particular motion so that the firmware can guarantee a particular mechanical position as long as the optical switch is open. An important philosophy here was to position each slotted rib (comb) at the "point of action" (the farthest point from the motor drive) so that backlash does not compromise the accuracy of the position detection.

By using relatively large (and inexpensive) motor drive ICs operating well within their thermal specifications and mounting the printed circuit assembly vertically for optimum convection cooling, thermal problems were avoided. For the picking action, an oversized solenoid is operated conservatively so that it does not get too hot. The solenoid delivers a relatively large force for the picker fingers but for short durations (less than two seconds).

The front-panel printed circuit assembly is connected to the main controller printed circuit assembly by a flexible circuit. Mounted on the front-panel printed circuit assembly are the three front-panel switches, the door open optoswitch, three LEDs, and the LCD. The LCD is a custom design procured with a standard driver IC on its flexible circuit, which is soldered to the front-panel printed circuit assembly. All of these components were physically modeled in the HP ME30 CAD system to integrate the electrical and mechanical designs.

An important design goal was ease of access to the printed circuit assembly since the firmware is stored in an OTP device that must be replaced if firmware upgrades are necessary. To this end the board is fully connectorized and fixed by a single screw. No adjustments or calibrations to the printed circuit assembly are needed, so complete printed circuit assemblies can be swapped in if necessary. The layout of the printed circuit board is heavily influenced by the flexible circuit designs and a lot of time in the early stages of the project was spent on the topography of the flexible circuits, their routing, and the effect of the positions and direction of entry on the printed circuit assembly layout. In particular, to keep the cost of the flexible circuits as low as possible they were all designed as single-sided circuits. This dictated pin ordering on the printed circuit assembly, which also needed to have minimum layers to keep it low in cost. The final printed circuit assembly has just four layers including power and ground planes covering 90% of the board area. There are four flexible circuits connecting the motions and the front-panel printed circuit assembly. Their physical layouts were modeled on the HP ME30 system and also using paper mock-ups to check for control of their positions when moving, as well as track layout.

> Greg K. Trezise Development Engineer Computer Peripherals Bristol

Ideas were tried in outline form to maximize the number of cartridges with the simplest mechanism. It quickly became clear that the size of the DDS cartridge imposed limitations that dictated the capacity and mechanism design. For example, even with minimal thicknesses in between, there is only

room for three cartridges above the drive. To achieve a capacity of four with a simpler mechanism the cartridges would have to move up and down in front of the drive, but this violated the form factor.

Using only mockups and cartridges, we arrived at the possibility of rotating the column of three tapes above the drive. This accommodated six cartridges and would make us the market leader in capacity. There is just space, but how could it be implemented? The vertical height of the components had to be pared down to the minimum. For example, there is 1.5 mm between cartridges, 1 mm for a shelf in the magazine, and 0.5 mm clearance (all dimensions nominal). The volume swept by the six tapes rotating is very large, taking up about half the height of the autoloader and most of the width, leaving only about 8 mm on each side. We decided that the changer mechanism would have to occupy some of the swept volume when the tapes were not rotating.

We used the HP ME30 mechanical CAD software to plan our air space and implement the concept. At this point three mechanical engineers developed the design, sharing the same file system and conventions so that we could easily load the subassemblies of our colleagues to check for clashes and interfaces.

#### **Autoloader Design**

The autoloader can be broken into several physical subassemblies, as follows:

- Magazine

- Mechanism motions—X, Y, Z, R

- Front panel and user interface

- Control electronics and motors

- · Mechanism firmware

- Drive firmware, SCSI interface, and link to the mechanism.

**Magazine.** The magazine is made from polycarbonate plastic moldings (see Fig. 2). It is simply a container for the six cartridges, three on each end. The main molding is a box structure into which some shelves are fixed.

**Fig. 2.** The six-cartridge magazine is designed to be handled like one large tape cartridge.

The thin (1 mm) wall sections and usability features made this an extremely challenging design. Required features were retention of the cartridges and acceptance of the correct orientation only. In other words, you can only put the cartridges into the magazine in the correct way, and then they stay in, even when you shake them by hand or apply shock and vibration to the unit. The cartridges were not designed with these features for autoloader use, so we had to be creative. In addition there are regulatory requirements (UL94-V2 flame resistance) and a need for reasonable robustness, that is, the cartridges should not be damaged if the magazine is dropped on the floor. The magazine also has areas for a label and indications to help ease of use. There is a gear form along one side for automatic loading. The magazine is shaped so that it can only be inserted the correct way into the autoloader.

A semitransparent polypropylene library case is supplied with the magazine. This allows the user to store the magazine neatly with some protection. It is similar to the library cases for commercial videotapes.

**X Motion.** Looking from the left side of the unit, the X motion moves horizontally (front to back) in the autoloader (see Fig. 3). This motion moves the cartridge horizontally. The

(continued on page 16)

**Fig. 3.** (a) Interior layout of the HP C1553A autoloader. (b) Motions of the cartridge changing mechanism.

## Autoloader Firmware Design

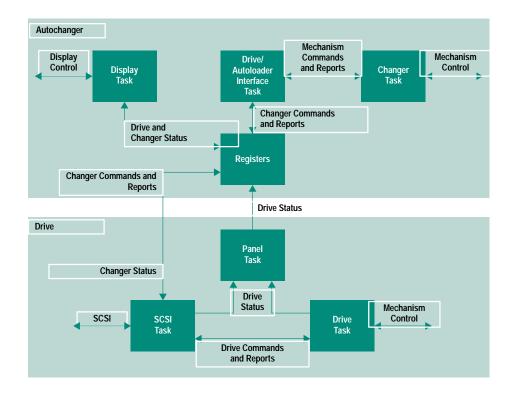

When the HP C1553A DDS-2 autoloader was designed, one of the primary goals was to add the autoloader mechanism to a standard DDS drive with no hardware modifications to the drive and minimum firmware modifications. The resulting architecture allows the autoloader mechanism to be independent of drive hardware and to be used with different drive products.

Originally, HP's DDS tape drive product line was not designed to be used with an autoloader. However, the requirement for a low-cost autoloader mechanism was realized and steps were taken to add an autoloader to the current product line. This required three basic steps:

- Design of the drive/autoloader interface, both hardware and software, requiring no hardware changes to the drive

- · Addition of the loader command set to the drive firmware

- Design of the autoloader electronics and firmware to enable the required communications with the drive.

#### Drive/Autoloader Interface

Since the drive had not been designed with the intention of interfacing to an autoloader, there was very little hardware available to create an interface to the autoloader mechanism. It was decided that a port that was used for debugging purposes in manufacturing test could be used to communicate with the autoloader, since it had no use outside the manufacturing line.

The port has four data lines and a single address line along with the required handshake lines for the drive's 68000 processor. This allows a total of four registers, two write-only and two read-only. It was decided that these should be 8-bit registers accessed by two successive 4-bit operations. The four registers are the drive status register, the autoloader status register, the drive autoloader command register, and the autoloader drive report register.

Two registers are used as a command report mechanism to allow the drive to send commands to the autoloader. This is the basis for the control of the autoloader. When the drive receives an SCSI command that requires autoloader operation, it writes the appropriate single-byte command code into the drive autoloader command register as two four-bit writes. When the autoloader has completed the operation it places the single-byte report in the autoloader drive report register and asserts an interrupt signal to the drive to indicate that the register should be read.

Commands that require parameters are preceded by a push parameter command. This is a single-byte command that has the top bit set. All other commands have the top bit clear. This allows the remaining seven bits to be pushed onto a parameter stack. Successive push parameter commands allow more than seven bits to be pushed.

The autoloader status and drive status registers are used for handling the front panel. Since the autoloader's front panel is completely different from the standalone drive's, it is accessed via the autoloader processor. However, since the drive processor has the responsibility for telling the autoloader what to do, the front-panel switches are read and interpreted by the drive via the autoloader status register. This allows maximum flexibility of operation and configuration.

To maximize the usability of the autoloader, it was decided to use a characterbased LCD display to give messages to the operator. Since most of the status information comes from the drive, the drive status register is used to pass status codes to the autoloader to display status messages on the display. The text for the messages is stored in the autoloader processor ROM. While it would have been more flexible to store the messages in the drive, there was insufficient space.

#### **Drive Firmware Architecture**

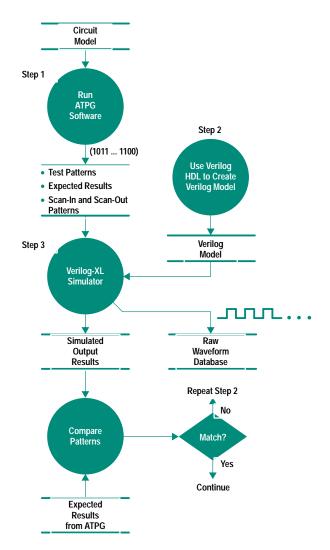

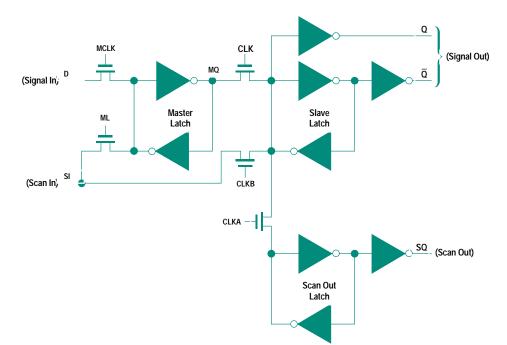

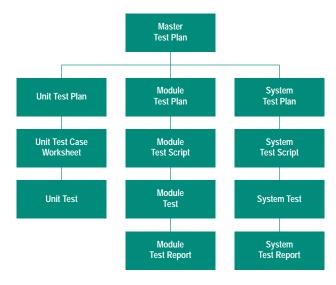

The changes required to the drive firmware to implement the drive/autoloader interface relate to two distinct areas. The architecture of the firmware for the autoloader is shown in Fig. 1.

First, the normal front-panel handling task within the firmware is replaced by a new version, which communicates drive status to the autoloader. This receives status information from both the SCSI task and the drive task on the drive. This status information is passed over the drive/autoloader interface rather than being displayed on the drive front panel. The SCSI task is changed to read the buttons on the new front panel as well as the eject button on the drive. The drive eject button is left active so that a tape can still be recovered from a drive in an autoloader even if the autoloader hardware is not working.

Secondly, the SCSI task required the addition of the functionality to handle the SCSI medium changer command set. This involved adding new functionality to the task to interpret a new class of commands and pass them on to the autoloader

Fig. 1. Autoloader firmware architecture.

mechanism. Parsing the commands on the drive allows the drive to remain in control of the whole autoloader and minimizes the risk of conflicting commands going to the drive and autoloader. It also avoids duplicating the software to parse SCSI commands for both the drive and the autoloader.

#### **Autoloader Firmware Architecture**

The autoloader firmware consists of three distinct functions. These are communicating over the interface to the drive, handling the display, and controlling the autoloader mechanism.

These three functions are implemented in three separate tasks running in a roundrobin fashion with a 1-ms time slice for each function. This made development of the software easier and allowed the separate functions to be implemented with minimal risk of interference with one another.

To save hardware costs, the drive/autoloader interface registers are not implemented as hardware latches. Instead, the I/O lines from the drive are wired directly into the ports of the H8/325 microcontroller used to control the autoloader mechanism. The H8 has a set of internal memory locations that mirror the imaginary hardware registers. When the select line from the 68000 is asserted, indicating an access to the drive/autoloader interface registers, this causes an interrupt to the H8. The H8 reads its I/O lines and handshakes the data to or from the 68000. This gives the appearance to the 68000 of slow hardware latches. The tasks running on the H8 merely need to access the internal memory locations as if they were the registers.

The drive status register is treated slightly differently from the other registers in the drive/autoloader interface. Because the drive can send repeated status values to this register faster than the display task on the H8 can read them, the values are queued within the H8 to be read in sequence. This ensures that an important status code is not lost behind a less important one. In addition, certain status codes cause flags to be set within the H8 that determine whether the drive is in a certain state. This allows tracking of the state of the drive.

Mark Simms

Development Engineer

Computer Peripherals Bristol

cartridge is gripped by metal fingers (mounted on a picker arm) on an edge near where a human grips the cartridge. The fingers are sprung shut, gripping a cartridge in case of a power failure, and are opened by a solenoid. The fingers are mounted on an arm, which pushes and pulls the cartridge. The arm can pull a cartridge out of the magazine and push it into the drive. The picker arm is moved by a belt, which is driven by a dc gear motor.

The cartridge is not designed for manipulation by a mechanism, so the choice of features that were suitable for gripping and alignment was limited. The obvious edges were not specified in the cartridge standard, and it took two years to have some of these features added to the standard.

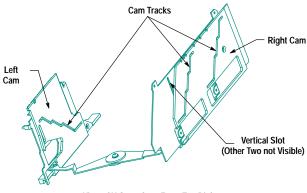

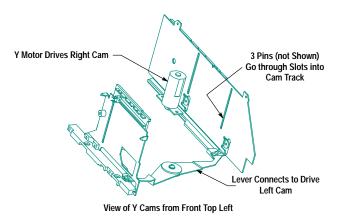

Y Motion. The Y motion moves the cartridge and picker arm up and down. The picker arm is mounted on a platform that is lifted or lowered by two cams. The picker arm runs on a shaft, allowing the X motion. The shaft and the other X-motion parts including the gear motor and belt are all mounted on the platform. Connections are made to these parts by a flexible circuit. The platform has three pins, one on the left and two on the right, which project out the sides (looking from the front of the unit) into cams, one on each side of the unit. The pins run in tracks that resemble escalator shapes, that is, they have 50-degree slopes with horizontal portions. The pins can only move vertically because they also run in slots in metal plates. The cams with the shaped slots

View of Y Cams from Front Top Right

**Fig. 4.** Y-motion cam design. (a) View of the Y cams from the front top right. (b) View of the Y cams from the front top left.

move backwards and forwards and drive the pins and the platform up and down (see Fig. 4). Both cams are driven by one dc gear motor. The one on the right has a molded rack and is driven directly by a gear on the gear motor. The left cam is connected by a lever across the bottom front of the unit to the right cam, and is driven by the same Y gear motor. This cam arrangement tolerates inaccurate positioning of the Y gear motor and cams. The height of the cam components themselves determines the height accuracy of the platform, which early calculations showed is adequate. The pins can be anywhere on the horizontal portions of the cam tracks, which are about 5-mm long. The flat plate arrangement of the cams and tracks fits neatly into the unit on either side of the platform. The left cam extends into the magazine rotation area making extra use of the space when the magazine is not rotating.

R Motion. The R motion is the rotation of the magazine. This is achieved by a large disk in the top of the unit. The magazine sits on top of the drive. The usual drive lid (top) is replaced with one that has the front edge cut away to allow the cartridge to be lifted straight up with the 11-mm overlap. The rotating disk in the top of the unit has two moldings attached to it that hang down on either side of the magazine, allowing it to be located and turned around. Originally the rotating disk in the top of the unit was going to be inside the unit. However, because of the extreme vertical space problems, the disk is actually part of the exterior surface of the unit. The disk rotates 180 degrees and is driven by a dc gear motor through a clutch. The clutch allows the disk to be

driven into an end stop for accuracy while preventing damage to the gear motor, which was found in early prototypes. The clutch is a custom design and drives a gear form on the disk.

**Z Motion**. The Z motion is the movement of the magazine in and out of the autoloader. The magazine has a large rack (gear form) on one side. This engages with a gear in the unit, which is driven, through a custom clutch, by the Z dc gear motor. A microswitch (Z switch) activated by a rocker arm indicates when a magazine has been inserted by the user. The insert and eject mechanism (Z motion) is deliberately designed to mimic the familiar home video recorder type of action. User tests showed that this action was familiar and intuitive. The action of the user is to push the magazine into the autoloader through the door, which is sprung shut. The Z switch detects the magazine and the Z gear motor starts. When the magazine is pushed a little farther the gear engages and pulls the magazine from the user. On entry the magazine compresses a spring-loaded pusher arm, which is used on ejection. The Z switch also detects when the magazine has reached the fully home position, that is, fully into the unit. On ejection the Z gear motor pushes the magazine out through the opened door. As the gear disengages, the sprung pusher completes the ejection. The magazine is caught by a small sprung plastic part to ensure a consistent eject distance. The distance is over 22 mm, which allows handicapped users to grip and remove the magazine.

The lid assembly, which contains the R and Z motions, was one of the later subassemblies designed and proved very difficult to finalize. The physical space restrictions and the desire to get the right feel for the user meant that several iterations of design had to be prototyped and tested.

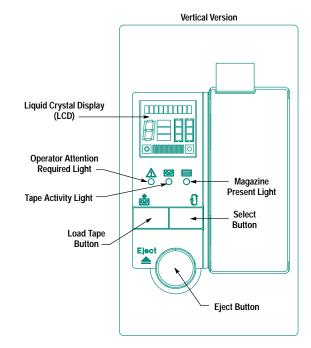

Front Panel. The front panel assembly provides the controls (three buttons), displays, and door (see Fig. 5). A printed circuit board mounted behind the front-panel plastic molding has the display and switch components on it. Once again space was at premium and the whole assembly had to be thin to miss other mechanism parts. The layout was determined by the user tests and the position of the door. The door is central in the upper portion. The entry has a keying feature so that the magazine cannot be inserted the wrong way. Combined with the magazine features, this means that the user is guided into correctly inserting the cartridges and prevented from making mistakes. This means that the correct orientation of the cartridge is ensured when it arrives inside the autoloader. This is not always the case in other autoloader systems, which have to check the orientation.

The door opens inwards and is sprung shut, but for magazine ejection the door must be opened by the unit to allow the magazine to eject. The door is locked when a magazine is inside the unit to prevent tampering or injury to the user. It is unlocked when there is no magazine inside to allow the user to insert one. The door is pushed open and locked by the movement of the left-hand cam. The cam travels are extended to allow this operation. At the normal resting Y height (bottom of travel in front of the tape drive), the cams move farther to unlock the door, then farther to push open the door. This allows the extra function with no extra gear motor or mechanism. An optoswitch sensor detects whether the door is open; its main purpose is for safety, so that the

Horizontal Version

Fig. 5. Front panel layout.

unit can be stopped in case of a faulty lock. In this case, the unit will display an error message, "Close Door," and wait.

The appearance and position of the front-panel displays and controls were determined by the industrial designer within the mechanical design limitations and were heavily influenced by the user test results. Early on, some mockups were tested because there is potentially a lot of information that could be displayed to the user, such as error messages and many status messages, about 60 total. The most basic button and the one that all users require is the **Eject** button. This was made large and obvious, the shape making it look pushable so that minimum or no text is needed for users to choose it. The second button selects a starting tape, of the ones loaded, and the final button starts a manual backup. Alternatively, the unit can be controlled by SCSI commands from the host computer.

The displays are grouped into two types: those giving overall status that can be seen from a distance, such as idle, backing

## Network Backup with the HP C1553A DDS Autoloader

The four main applications for the HP C1553A autoloader described in the accompanying article are:

- Single large backup

- Centralized network backup

- Fully automated backup

- Near-line data storage.

The backup of a large amount of data in a single session is a clear application for the autoloader. Today there are many servers with a disk capacity exceeding that of a single DDS-2 cartridge, which is typically 8 gigabytes with 2:1 data compression. The system administrator with a single tape drive must either manually insert new tapes into the drive when doing full backups, or must settle for incremental backups that only back up the data that has changed since the last full backup. These two options present some difficulties. Backups are typically carried out at night when server use is lower, so tape changing is inconvenient at best. A restore based on an incremental backup routine can be complicated since it will involve using several unrelated tapes. The autoloader, with its six cartridges, enables the system administrator to protect up to 48 gigabytes of data in one single unattended session.

Most of today's local area networks consist of several servers and many clients. Centralized network backup involves backing up all servers and clients across the network onto one high-capacity drive such as the autoloader. This is a cheaper alternative to having a separate tape drive on each server. Other benefits include having only one tape drive and one software package to administer and enhance security by having all removable data in one location, which can be physically secured. This is the same rationale that has been employed for centralizing network printing on one high-duty-cycle printer. For additional flexibility each of the the autoloader's six cartridges can be configured to hold data from a specific source. For example, each server can be backed up to its own cartridge and all clients to one of the other cartridges. Alternatively, all servers and clients on a segment of the network can be backed up to a specific cartridge. The exact choice will depend on restore and disaster recovery considerations.

Fully automated backup relieves the busy system administrator from another task previously taken for granted in the days of central mainframes: tape rotation. Methods such as "grandfather-father-son" and "tower of Hanoi" were developed to prevent overuse and wearout of media and to make available several differently aged versions of data when restoring. These methods involve backing up to a different cartridge every day. For the system administrator with a single tape drive this means manually changing the tape in the drive every day. If for some reason this does not happen most software packages will abort the backup, meaning that the system is unprotected. More significant, when the time comes for a restore, the system administrator must be on hand to retrieve the correct cartridge from secure storage and manually load it into the drive. These tasks can now be automated by making use of the autoloader's multiple-cartridge capacity. A simple routine with five data cartridges and a cleaning cartridge could be configured to perform a full backup every weekday to a new tape. This weekly cycle could be repeated over an extended period of time. A routine giving a longer file history would involve performing a full backup on the first day of the week, followed by daily incremental backups to the same tape. The magazine would then provide five weeks of protection for a server of up to five gigabytes. Using a tower of Hanoi rotation scheme, sixteen weeks of protection can be achieved with a single magazine. In all cases, the only manual intervention would be periodic magazine rotation to a fireproof safe or offsite location. Restores no longer need to involve the system administrator, either. With all of the cartridges available by random access in the magazine, the backup software can give users the ability to restore their own files with overall access rights controlled by the system administrator.

Prolonged operation of tape drives without any tape head cleaning can result in a media warning that causes the backup software to abort the backup. This need not be the case with the DDS-2 drive, which has a has a self-diagnostic capability that senses the write error rate. When this increases beyond a conservative threshold, the drive sends a message to the backup software, which can respond with the initiation of a head cleaning cycle using the cleaning cartridge included in the magazine. This will typically occur every twenty-five hours of use and ensures a long period of error-free operation without system administrator intervention.

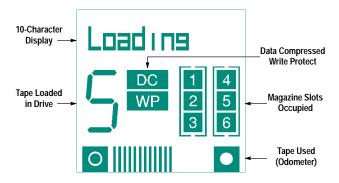

up, or fault condition, and those giving further detailed information that is required when the user is near the unit, such as "Insert Mag" or "Clean Me." A custom LCD was selected for the detailed information, the custom icons and layout enabling a lot of information to be conveyed at a glance without long text messages. Ten characters of text are available to display messages (see Fig. 6). The printed icons beside the three buttons and three LEDs were also developed and tested for intuitive use by users and to avoid any text that would require localization. The exception to this is that the word "Eject" was required by the English speakers tested because the universal eject icon, seen on almost every VCR

Fig. 6. Liquid crystal display layout.

and cassette player, was not recognized! The word "Eject" is acceptable internationally.

**Control Electronics.** This development effort is described in "Autoloader Control Electronics" on page 13.

**Mechanism and Drive Firmware.** This development effort is described in "Autoloader Firmware Design" on page 15.

#### **Mechanical Design Methods**

ME30, HP's 3D computer-aided design tool, was used by the mechanical and manufacturing engineers. It was run on HP 9000 Series 700 workstations that had a common disk mounted with directories structured and named like the product subassemblies. The designers were responsible for maintaining the latest revision of their parts in these shared areas, and for providing a macro that would simply load all the subassembly parts. The motors, the flexible circuits, and the main components on the controller printed circuit assembly were all modeled. Thus the latest design was available to the designers for cross-checking, and to the procurement and manufacturing engineers for process planning. HP ME30 proved very valuable at speeding up the checking and success of prototype assembly builds. Better visualization allowed the designers to spot problems early, thereby avoiding embarrassing problems on prototype builds. On one occasion, we discovered that we were about to design a gear motor assembly through the center of the H8 microprocessor!

aaaxsNear-line data storage is an evolving application for multiple storage devices based on using intelligent data management software known as Hierarchical Storage Management software. The size of hard disk mass storage on servers is increasing all the time. Today's average network server has a disk capacity of 9 gigabytes and this is projected to rise to 40 gigabytes within the next five years. The system administrator faces a constant challenge to ensure economic and efficient use of disk space by users. The reason for not adding hard disk drive capacity at will is cost. Hard disks are a very expensive data storage medium, but are necessary to ensure fast access to data; access time is of the order of 10 milliseconds. Magnetic tape, by contrast, has a cost per megabyte of data onehundredth that of hard disks, but the access time of a tape drive is on the order of 30 seconds. An analysis of the use pattern of files on a typical server shows that some current files are accessed frequently, but that the majority are older files used infrequently. Hierarchical Storage Management software tracks file access and automatically migrates infrequently used files to a lower-cost storage medium. Although the file is stored on another device, a phantom file of zero size is left in the original directory. As far as the user is concerned the file is still present. When access is required the Hierarchical Storage Management software retrieves it automatically. The small delay in retrieving the file from the slower device is acceptable on an occasional basis. All of the activity is transparent to the users, who effectively see a virtually unlimited amount of disk space. The data migration is triggered at typically 80% of disk capacity. The system administrator therefore never needs to be concerned about running out of disk space. The autoloader with its six cartridges can provide up to 48 gigabytes of near-line data storage at a fraction of the equivalent hard disk storage cost.

#### **Performance Considerations**

The autoloader's large capacity is well-matched by the DDS-2 drive's high data transfer rate. However, backup is a resource intensive operation that uses all of the components of the computer and network, not just the tape drive. Careful selection of all of the hardware is required to balance the throughput and ensure that there are no bottlenecks. The exact configuration will depend on the type of backup being performed.

For server-based backup, the limiting component is typically the hard disk drive. Backup involves randomly accessing all files on the hard disk. The disk can spend

more time seeking data than actually reading it. The limitation can be reduced by "spanning" the data to be read over several disks. While one or more disks are seeking data one of the other disks can be reading data. This spanning can usually be implemented in the operating system but is more commonly implemented in hardware in the form of a redundant array of inexpensive disks (known as a RAID disk array). Here a dedicated controller card takes care of all the data input and output for all of the disks and frees the operating system from that overhead. In most cases an HP C1533A DDS-2 tape drive backing up data from a RAID disk array with five disks will approach its maximum native transfer rate of 510 kilobytes per second which is equivalent to 60 megabytes per minute with data compression.

For centralized network backup, the limiting component is typically the network. Today's most popular network topology is Ethernet, operating at a bandwidth of 10 megabits per second. During backup all the data must travel across the network, along with all of the disk access commands. This results in most cases in a transfer rate of about half of the maximum the DDS-2 drive can achieve. This can be reduced further if the amount of traffic on the network is high enough to result in packet collisions, so backups should be run at night when traffic is low. To achieve higher transfer rates over the network, faster topologies must be used. FDDI over fiber-optic cable and 100 Base-VG both operate at 100 megabits per second, ten times faster than Ethernet. Implementation of these technologies is becoming more widespread for reasons other than backup, such as multimedia and video. For existing installations it is not necessary to recable the entire network. The majority of data transferred will be from server to server, so these can be connected together with a dedicated high-speed backbone. This will result in a backup speed close to the DDS-2 drive's maximum.

When using intelligent data management software, an apparent increase in performance can be seen. This is because the infrequently accessed files, after having been backed up several times, are considered stable and are no longer backed up. A full backup therefore involves fewer files and can be completed in a shorter time. This performance gain is achieved with software without any changes to the hardware

Michael G. Bertagne Technical Marketing Engineer Mass Storage Europe

Although valuable, the latest HP mechanical CAD software does not fully simulate all the mechanical motions. In this respect it is less mature than EE CAD. So the traditional design, build, test, redesign cycle is still the major way to achieve reliability improvements in the design. Anything that can be done to shorten this cycle, rapid prototyping for example, can save weeks or months of time to market. The 3D models allowed us to use the latest fast prototyping methods, including stereo lithography and CNC milling of parts.

#### **Design Margin Analysis**

Because of the desire to prove as much of the design as possible before commitment to tooling, we adopted an unusual approach to the mechanical tolerances. Typically designers will approach key areas and perform a tolerance analysis. They will add up the tolerances for the parts using data that they hope is representative of the production parts. Because of the lack of space, interdependency of all the subassemblies, and simply pressure of work on the designers, we decided to adopt another approach. A consultant from Cranfield Institute of Technology, one of the leading teaching and consultancy groups in manufacturing technology in the UK, was enlisted to help analyze the tolerances. We started from the outside in, deciding on the key areas of functionality, then building up spreadsheets of the systems with the tolerances. Our procurement engineers provided capability study data for the manufacturing processes of similar parts.

Starting out with simple arithmetic, we built this analysis into a design margin index. 1 The managers and designers were then able to have a single number for the "goodness" of the design in each of six key areas. This was obtained by the root-sum-of-squares (RSS) method of calculating tolerances.<sup>2</sup> The squares of the tolerances are all added, and then the square root of the sum gives the variance of the assembly. If we had simply taken worst-case tolerances the design would not have worked because the worst-case numbers were too large. The RSS method assumes that the parts have a typical Gaussian distribution of sizes. Statistically, taking the RSS only excludes 0.27% of the possible cases. This was not considered completely satisfactory, so our goal was to have 1.5 times the RSS figure as the minimum design criterion for each key area. A simple scoring method of comparing the actual RSS figure for the key area with the goal of 1.5RSS gave us the "goodness" figure. Because the key areas are not independent, this allowed us to view the overall capability of the design and prevented conflicts such as improvements by a designer in one area increasing margin at the expense of another key area.

The use of a consultant to check the design and the use of the design margin index strengthened our execution of the mechanical design, forcing us to change the design and production processes of some parts.

#### A Change of Direction

As the design approached completion and we were ready to start production prototypes in manufacturing, the division reassessed the manufacturing strategy. It was clear that the product would consume more resources than the division was willing to commit. The increase in volumes of the DDS-1 products and the launch of the DDS-2 drive at nearly the same time would cause a bulge in resource requirements. The decision was made to find a partner to manufacture the autoloader mechanism, while HP supplied the DDS-2 drive.

Büro-und DatenTechnik (BDT) GmBH was selected and from November 1992 worked closely with us to take the autoloader into manufacturing. BDT was selected for their manufacturing expertise and quality in producing similar products, including paper sheet feeders for printers and another autoloader. The partnership has proved extremely successful. Their engineers have looked critically at the design and improved it. They have developed it and taken it successfully into manufacturing. HP was able to redeploy people on other projects, leaving only a core team to work with BDT.

#### **Applications**

To ensure the availability of software solutions that fully support the automation features of the HP C1553A, HP has developed the LABS (Low-Admin Backup for Servers) standard guidelines for software developers. The LABS guidelines define a set of software attributes that virtually eliminate human operator involvement in the backup process. The HP SureStoreTape 1200e product is available as a bundle with LABS software developed by Palindrome Corporation. In addition, several other solutions are available for different operating systems, such as Cheyenne ARCSERVE and Palindrome Backup Director for Novell networks, Arcada Backup Exec for Windows NT, and Legato NetWorker for UNIX® systems and Novell.

The autoloader can work in two ways, depending on the application software: random mode or sequential mode. In random mode the software issues SCSI medium changer commands to load a specific cartridge number. The software therefore has complete control over the operation. In sequential mode the user starts the backup from the chosen

cartridge, say cartridge 1, and the host writes until the tape is full. The host then issues an SCSI unload command and the autoloader replaces the cartridge with the next one automatically. This allows easier integration into older systems that do not support the SCSI medium changer command set.

See page 18 for more about network backup applications.

#### Acknowledgments

The core team of designers deserves a lot of credit for achieving so much with so little: a small volume in the product, and a small team compared to the size of the job. Everyone contributed a lot. Thanks to Ray Dixon and Phil Williams for mechanical design, Mark Simms for mechanism firmware, Nigel Evans for displays, and Kevin Jones for drive and SCSI firmware. Bill Meikle, R&D project manager, guided us and contributed many important ideas. Jim Dow did the industrial design and he and Tom Cocklin, both from the HP Greeley facility, heavily influenced the ergonomics. Jeff Blanchard tried to break the prototypes to the best effect and guided us toward a reliable design. Outside this team of designers was the strength of our procurement and manufacturing engineers, especially Phil Catt, Dave Rush, and Roy Bradford, who enabled us to turn prototypes around and also contributed to the design. Dr. John Adie (design margin index) and Dave Moseley from Cranfield Institute of Technology provided an injection of ideas and analysis.

We must give a special mention to the BDT engineers and production personnel who took our basic design, criticized and improved it. They put in much hard effort and good faith to get the product into manufacturing.

#### References

- 1. J. Adie, "Optimising the Design Process," *Professional Engineering*, February 16, 1994.

- 2. J.R. Milner, "The Toleranced Design of the Model 520 Computer," *Hewlett-Packard Journal*, Vol. 35, no. 5, May 1984, pp. 10-11.

Windows is a U.S. trademark of Microsoft Corporation.

UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open\* Company Limited.

$\label{prop:company} \mbox{\sc Limited in the UK and other countries.}$

# **Automatic State Table Generation**

The HP C1553A DDS tape autoloader requires a complex sequence of simple operations to carry out mechanical retries. These sequences are defined in tables. Cadre's Teamwork was used for input and an automatic tool was used to generate the tables to go in ROM.

#### by Mark J. Simms

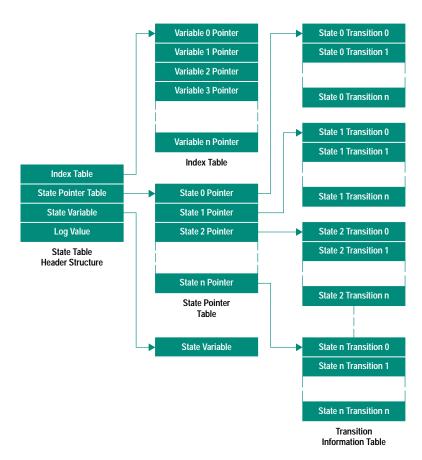

The autoloader firmware for the HP C1553A digital audio tape autoloader was written in the C programming language to run on a Hitachi H8/325 processor. This processor is an embedded system microcontroller with built in ROM, RAM, I/O ports, timers, and serial ports. This allows a very low-cost implementation of the autochanger controller in which most of the functions can be carried out in a single chip. However, the largest ROM size available on the H8 series of processors was 32K bytes. This means that the complex retry algorithms required for controlling such a mechanical device needed to be implemented in as compact a manner as possible.

Our laboratory has a large amount of experience in producing table-driven systems. All of our products have had some form of table-driven control structures in some part of their firmware. However, experience had shown that there can be severe problems maintaining table-driven code because of the difficulty of maintaining the tables. This derives from the lack of readability of software written in C or assembly language that merely defines the contents of data structures. A lot of documentation needs to be added to the source code to explain the meaning of the entries. If this is not maintained, then the declarations rapidly become unreadable. This greatly increases both the time needed to implement changes and the risk of errors.

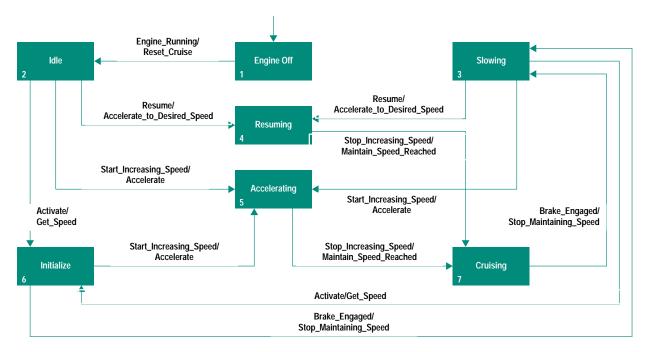

The designers of the HP 9145A cartridge tape drive and the HP 35470A DDS tape drive attempted to improve this situation by defining state machine languages that can be translated into C source code automatically. These languages offered powerful constructs for defining the tables in terms of state machines. The software would remain in one state until an event was detected. Then a set of actions would be carried out and a new state entered. This approach made the table definition much more readable than the basic data declarations and greatly alleviated the maintenance problems. However, the state machine languages suffered from many of the problems that are characteristic of "unstructured" programming techniques. There was no observable flow in the source code since transitions were permitted between any two states. This made it very difficult to follow the flow of the program and determine what sequence of actions had occurred.

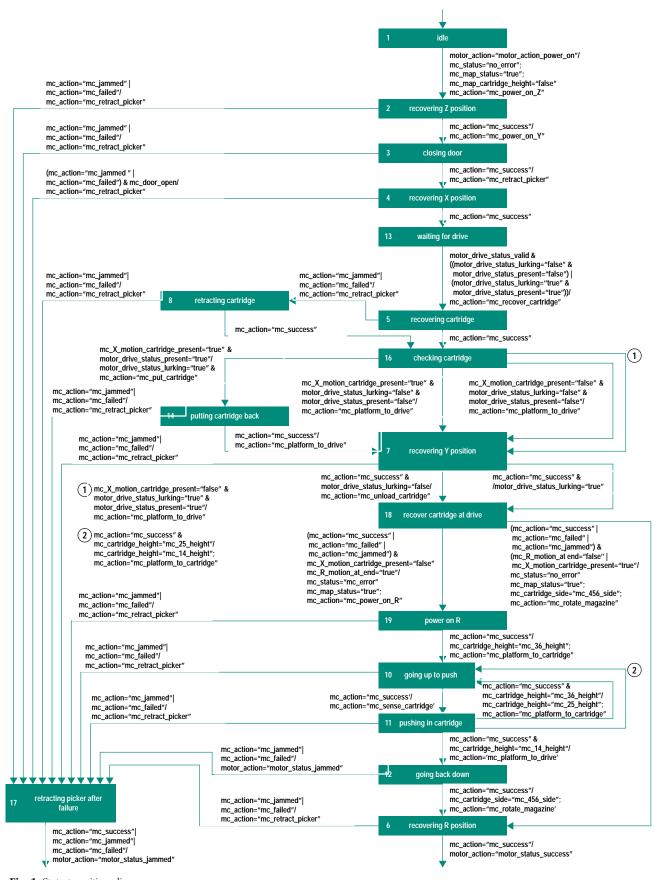

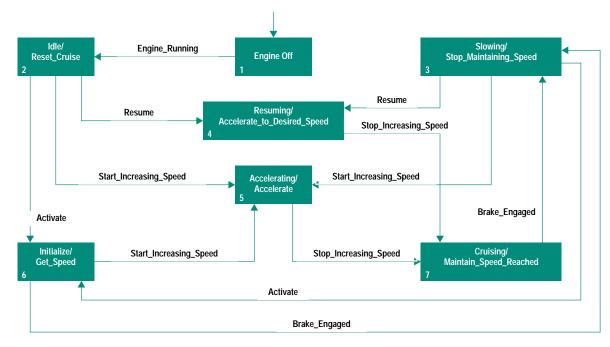

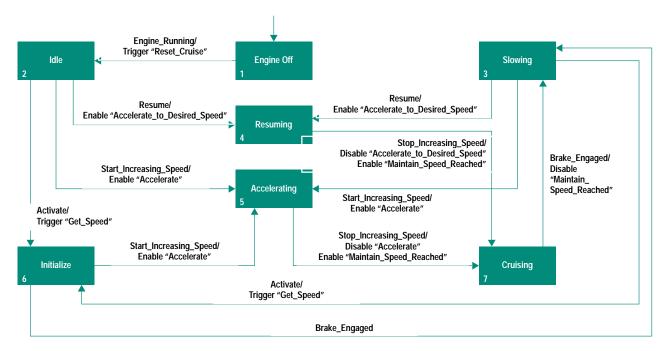

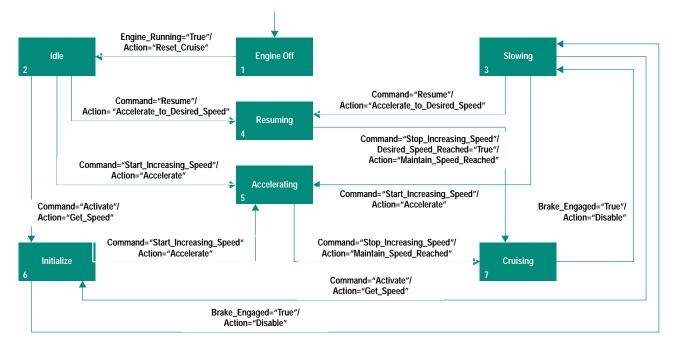

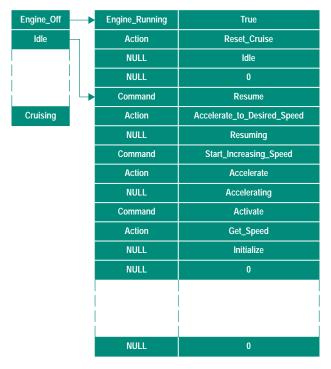

To aid in documenting these state machines, the Teamwork structured analysis tool from Cadre Technologies was adopted. This allowed the initial problem analysis to be carried out graphically. A state transition diagram was produced

to document the desired solution (see Fig. 1). This was then implemented using the state machine language. However, as the state machine language description was modified, the diagram gradually became more and more out of date and was updated periodically. This meant that while the diagram could be used to gain an initial familiarity with the software, it could never be guaranteed to be completely accurate.

With the HP C1553A autoloader, these problems became more serious. The state tables were to be used very extensively for mechanical control. Also, there was a very strong need to communicate the control algorithms to mechanical engineers and the product test team. This required that good accurate documentation be available to all within the division. It was felt that any manual system for maintaining such documentation would prove unusable in real situations. As a result, a decision was made to generate the state tables directly from the Teamwork diagrams. This would ensure that the diagrams were always accurate reflections of the software.

#### **Design Implications**

Analysis of the HP C1553A motor control software showed that the software divides into two major sections. The first is a number of routines that handle the low-level control of the mechanism. These routines control the motors and solenoids, read sensors, and track the position of the mechanism. They track control information and map that onto the control signals required to operate the motors in the correct direction at the correct power level. They debounce input readings and map them into mechanism position information. These routines are implemented in C and use global variables to interface with the rest of the software. The routines are called in sequence to carry out all the necessary interfacing to the mechanism.

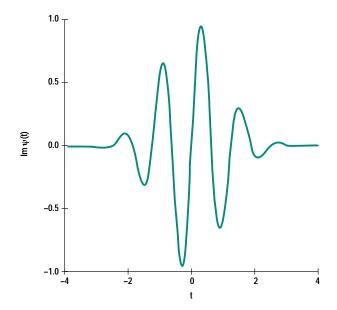

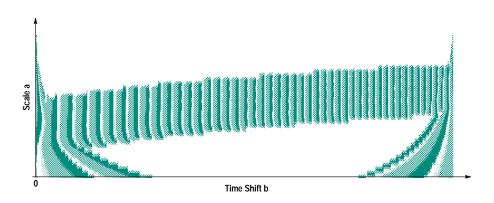

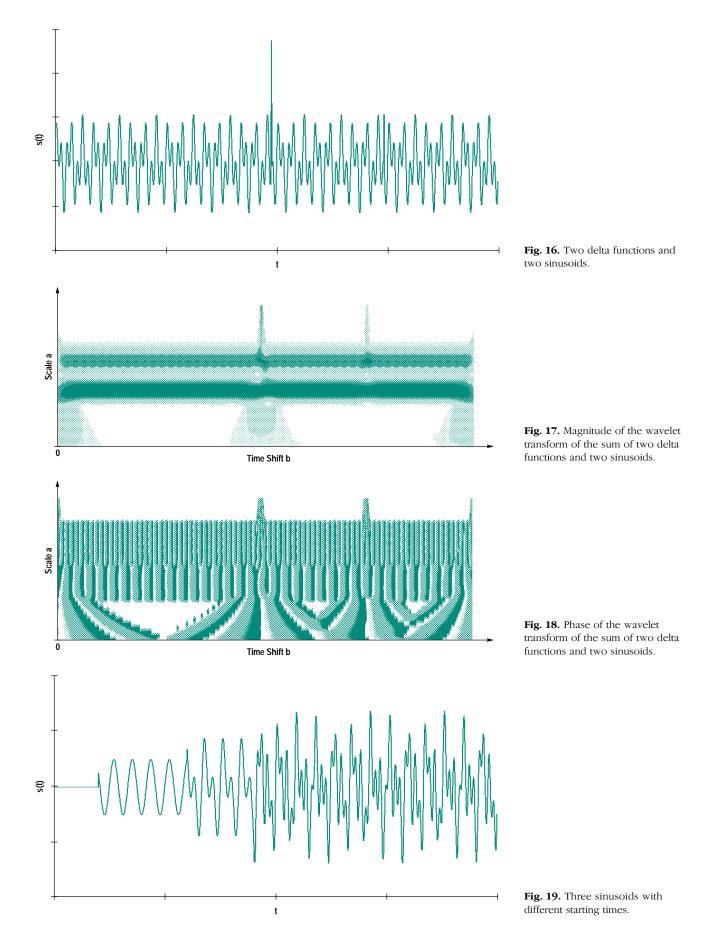

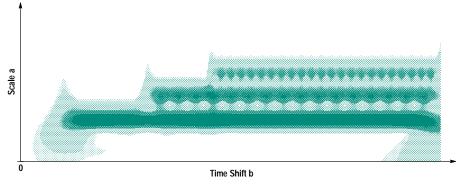

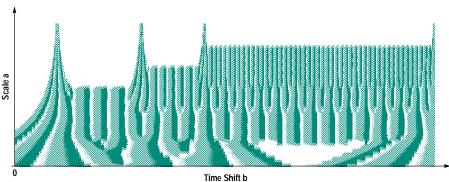

The second section is the control sequencing. This contains a number of state machines. Some of these are directly linked to the individual mechanism parts. Others sequence individual mechanism operations together in response to a single command. These state machines interface with the low-level routines by means of the control information and mechanism position global variables.